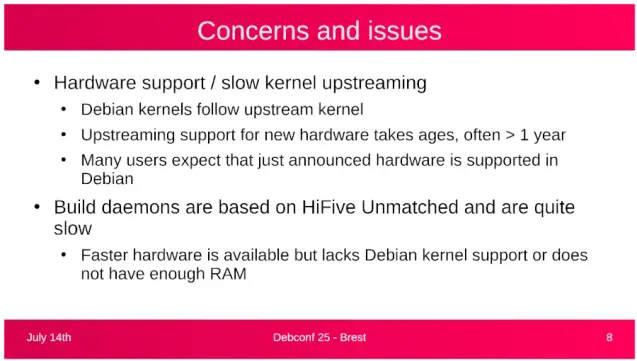

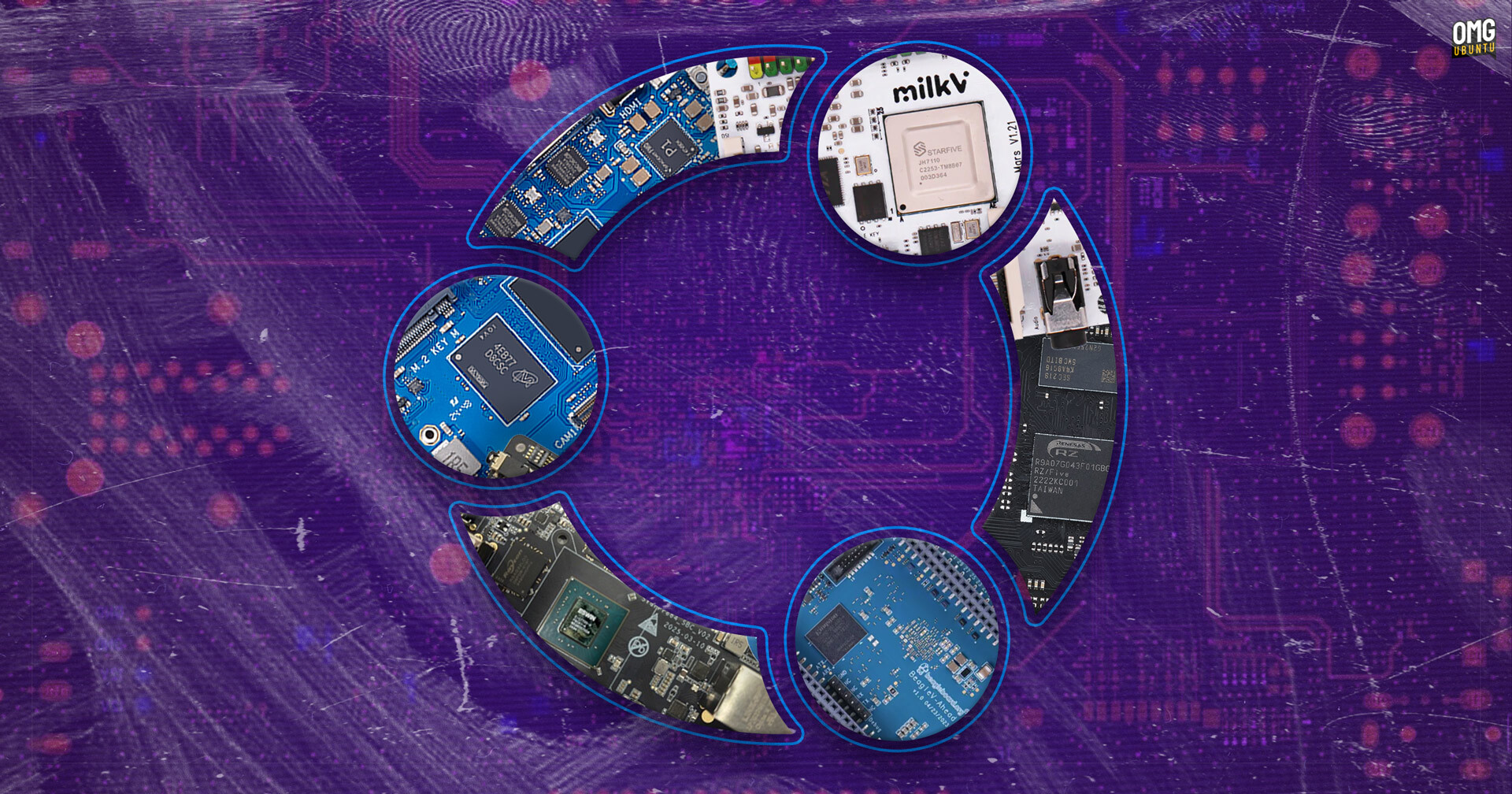

With the #Linux #Debian 13.0 release planned for 9 August, one of the notable fundamental features with this Debian "Trixie" release is now supporting #RISC-V as an official #CPU architecture. This is the first release where RISC-V 64-bit is officially supported by Debian Linux albeit with limited board support and the Debian RISC-V build process is handicapped by slow #hardware